# SMALL-OUTLINE DDR SDRAM DIMM

D400SB1G\_M - 1GB 16 chips

For the latest data sheet, please visit the Super Talent Technology web site: www.supertalent.com

## Features

- 200-pin, small-outline, dual in-line memory module (SODIMM)

- Fast data transfer rates: PC3200

- Utilizes 400 MT/s DDR SDRAM components

- 1GB 128 Meg x 64

- VDD = VDDQ = +2.6V

- 2.6V I/O (SSTL\_2 compatible)

- VDDSPD = +2.3V to +3.6V

- Commands entered on each positive CK edge

- DQS edge-aligned with data for READs; centeraligned with data for WRITEs

- Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

- Bidirectional data strobe (DQS) transmitted/ received with data—i.e., source-synchronous data capture

- Differential clock inputs CK and CK#

- Four internal device banks for concurrent operation

- Programmable burst lengths: 2, 4, or 8

- Auto precharge option

- Auto Refresh and Self Refresh Modes

- 7.8125µs maximum average periodic refresh interval

- Serial Presence Detect (SPD) with EEPROM

- Programmable READ CAS latency

- Gold edge contacts

## Table 1: Address Table

|                          | 1GB                |

|--------------------------|--------------------|

| Refresh Count            | 8K                 |

| Device Row Addressing    | 8K (A0–A12)        |

| Device Bank Addressing   | 4 (BA0, BA1)       |

| Device Configuration     | 512Mb (64 Meg x 8) |

| Device Column Addressing | 2K (A0–A9, A11)    |

| Module Rank Addressing   | 2 (SO#, S1#)       |

# Figure 1: 200-Pin SODIMM

## 16 chip memory module designs

1.50in (38.10mm)

Revision DFC 03/06 version: b Products and specifications discussed herein are subject to change without notice. © 2006 Super Talent Technology, Corp.

| PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL |

|-----|--------|-----|--------|-----|--------|-----|--------|

| 1   | VREF   | 51  | Vss    | 101 | A9     | 151 | DQ42   |

| 3   | Vss    | 53  | DQ19   | 103 | Vss    | 153 | DQ43   |

| 5   | DQ0    | 55  | DQ24   | 105 | A7     | 155 | Vdd    |

| 7   | DQ1    | 57  | Vdd    | 107 | A5     | 157 | VDD    |

| 9   | Vdd    | 59  | DQ25   | 109 | A3     | 159 | Vss    |

| 11  | DQS0   | 61  | DQ\$3  | 111 | A1     | 161 | Vss    |

| 13  | DQ2    | 63  | Vss    | 113 | Vdd    | 163 | DQ48   |

| 15  | Vss    | 65  | DQ26   | 115 | A10    | 165 | DQ49   |

| 17  | DQ3    | 67  | DQ27   | 117 | BA0    | 167 | Vdd    |

| 19  | DQ8    | 69  | Vdd    | 119 | WE#    | 169 | DQS6   |

| 21  | Vdd    | 71  | DNU    | 121 | S0#    | 171 | DQ50   |

| 23  | DQ9    | 73  | DNU    | 123 | NC     | 173 | Vss    |

| 25  | DQS1   | 75  | Vss    | 125 | Vss    | 175 | DQ51   |

| 27  | Vss    | 77  | DNU    | 127 | DQ32   | 177 | DQ56   |

| 29  | DQ10   | 79  | DNU    | 129 | DQ33   | 179 | Vdd    |

| 31  | DQ11   | 81  | Vdd    | 131 | Vdd    | 181 | DQ57   |

| 33  | Vdd    | 83  | DNU    | 133 | DQS4   | 183 | DQS7   |

| 35  | CK0    | 85  | NC     | 135 | DQ34   | 185 | Vss    |

| 37  | CK0#   | 87  | Vss    | 137 | Vss    | 187 | DQ58   |

| 39  | Vss    | 89  | DNU    | 139 | DQ35   | 189 | DQ59   |

| 41  | DQ16   | 91  | DNU    | 141 | DQ40   | 191 | VDD    |

| 43  | DQ17   | 93  | Vdd    | 143 | Vdd    | 193 | SDA    |

| 45  | Vdd    | 95  | CKE1   | 145 | DQ41   | 195 | SCL    |

| 47  | DQS2   | 97  | NC     | 147 | DQS5   | 197 | VDDSPD |

| 49  | DQ18   | 99  | A12    | 149 | Vss    | 199 | NC     |

# Table 2: Pin Assignment(200-Pin SODIMM Front)

# Table 3: Pin Assignment (200-Pin SODIMM Back)

| PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL |

|-----|--------|-----|--------|-----|--------|-----|--------|

| 2   | VREF   | 52  | Vss    | 102 | A8     | 152 | DQ46   |

| 4   | Vss    | 54  | DQ23   | 104 | Vss    | 154 | DQ47   |

| 6   | DQ4    | 56  | DQ28   | 106 | A6     | 156 | Vdd    |

| 8   | DQ5    | 58  | Vdd    | 108 | A4     | 158 | CK1#   |

| 10  | Vdd    | 60  | DQ29   | 110 | A2     | 160 | CK1    |

| 12  | DM0    | 62  | DM3    | 112 | A0     | 162 | Vss    |

| 14  | DQ6    | 64  | Vss    | 114 | Vdd    | 164 | DQ52   |

| 16  | Vss    | 66  | DQ30   | 116 | BA1    | 166 | DQ53   |

| 18  | DQ7    | 68  | DQ31   | 118 | RAS#   | 168 | Vdd    |

| 20  | DQ12   | 70  | Vdd    | 120 | CAS#   | 170 | DM6    |

| 22  | Vdd    | 72  | DNU    | 122 | S1#    | 172 | DQ54   |

| 24  | DQ13   | 74  | DNU    | 124 | NC     | 174 | Vss    |

| 26  | DM1    | 76  | Vss    | 126 | Vss    | 176 | DQ55   |

| 28  | Vss    | 78  | DNU    | 128 | DQ36   | 178 | DQ60   |

| 30  | DQ14   | 80  | DNU    | 130 | DQ37   | 180 | Vdd    |

| 32  | DQ15   | 82  | Vdd    | 132 | Vdd    | 182 | DQ61   |

| 34  | Vdd    | 84  | DNU    | 134 | DM4    | 184 | DM7    |

| 36  | Vdd    | 86  | DNU    | 136 | DQ38   | 186 | Vss    |

| 38  | Vss    | 88  | Vss    | 138 | Vss    | 188 | DQ62   |

| 40  | Vss    | 90  | Vss    | 140 | DQ39   | 190 | DQ63   |

| 42  | DQ20   | 92  | Vdd    | 142 | DQ44   | 192 | Vdd    |

| 44  | DQ21   | 94  | Vdd    | 144 | Vdd    | 194 | SA0    |

| 46  | Vdd    | 96  | CKE0   | 146 | DQ45   | 196 | SA1    |

| 48  | DM2    | 98  | NC     | 148 | DM5    | 198 | SA2    |

| 50  | DQ22   | 100 | A11    | 150 | Vss    | 200 | Vss    |

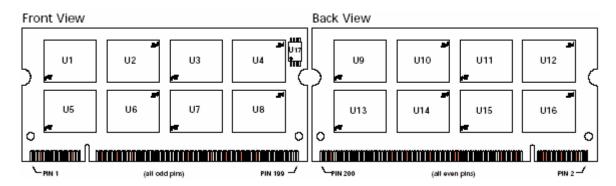

# Figure 2: Module Layout

## Table 4: Pin Descriptions

Pin numbers may not necessarily correlate with symbols. Refer to Pin Assignment tables on page 2 for more information.

| PIN NUMBERS                                                         | SYMBOL                 | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 118, 119, 120                                                       | WE#,<br>CAS#,RAS#      | Input            | Command Inputs: RAS#, CAS#, and WE# (along with S#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 35, 37, 158, 160                                                    | CK0, CK0#<br>CK1, CK1# | Input            | Clock: CK, CK# are differential clock inputs. All address and<br>control input signals are sampled on the crossing of the<br>positive edge of CK, and negative edge of CK#. Output data<br>(DQs and DQS) is referenced to the crossings of CK and CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 95, 96                                                              | CKEO, CKE1             | Input            | Clock Enable: CKE HIGH activates and CKE LOW deactivates the<br>internal clock, input buffers and output drivers. Taking CKE<br>LOW provides PRECHARGE POWER-DOWN and SELF REFRESH<br>operations (all device banks idle), or ACTIVE POWER-DOWN<br>(row ACTIVE in any device bank). CKE is synchronous for<br>POWER-DOWN entry and exit, and for SELF REFRESH entry.<br>CKE is asynchronous for SELF REFRESH exit and for disabling<br>the outputs. CKE must be maintained HIGH throughout read<br>and write accesses. Input buffers (excluding CK, CK# and CKE)<br>are disabled during POWER-DOWN. Input buffers (excluding<br>CKE) are disabled during SELF REFRESH. CKE is an SSTL_2 input<br>but will detect an LVCMOS LOW level after VDD is applied and<br>until CKE is first brought HIGH. After CKE is brought HIGH, it<br>becomes an SSTL_2 input only. |

| 121, 122                                                            | SO#, S1#               | Input            | Chip Selects: S# enables (registered LOW) and disables<br>(registered HIGH) the command decoder. All commands are<br>masked when S# is registered HIGH. S# is considered part of<br>the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 116, 117                                                            | BA0, BA1               | Input            | Bank Address: BA0 and BA1 define to which device bank an<br>ACTIVE, READ, WRITE, or PRECHARGE command is being<br>applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 99, 100, 101, 102, 105,106,<br>107, 108, 109, 110, 111, 112,<br>115 | A0-A12                 | Input            | Address Inputs: Provide the row address for ACTIVE commands,<br>and the column address and auto precharge bit (A10) for<br>READ/WRITE commands, to select one location out of the<br>memory array in the respective device bank. A10 sampled<br>during a PRECHARGE command determines whether the<br>PRECHARGE applies to one device bank (A10 LOW, device bank<br>selected by BA0, BA1) or all device banks (A10 HIGH). The<br>address inputs also provide the op-code during a MODE<br>REGISTER SET command. BA0 and BA1 define which mode<br>register (mode register or extended mode register) is loaded<br>during the LOAD MODE REGISTER command.                                                                                                                                                                                                          |

| 195                                                                 | SCL                    | Input            | Serial Clock for Presence-Detect: SCL is used to synchronize the presence-detect data transfer to and from the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 194, 196, 198                                                       | SA0-SA2                | Input            | Presence-Detect Address Inputs: These pins are used to<br>configure the presence-detect device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 193                                                                 | SDA                    | Input/<br>Output | Serial Presence-Detect Data: SDA is a bidirectional pin used to<br>transfer addresses and data into and out of the presence-<br>detect portion of the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12, 26, 48, 62, 134, 148, 170,<br>184                               | DM0-DM7                | Input            | Data Write Mask. DM LOW allows WRITE operation. DM HIGH<br>blocks WRITE operation. DM lines do not affect READ<br>operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11, 25, 47, 61, 133, 147, 169,<br>183                               | DQS0-DQS7              | Input/<br>Output | Data Strobe: Output with READ data, input with WRITE data.<br>DQS is edge-aligned with READ data, centered in WRITE data.<br>Used to capture data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Table 5: Pin Descriptions (continued)

Pin numbers may not necessarily correlate with symbols. Refer to Pin Assignment tables on page 2 for more information.

| PIN NUMBERS                                                                                                                                                                                                                                                                                                    | SYMBOL   | TYPE             | DESCRIPTION                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| 5, 6, 7, 8, 13, 14, 17, 18, 19,<br>20, 23, 24, 29, 30, 31, 32, 41,<br>42, 43, 44, 49, 50, 53, 54, 55,<br>56, 59, 60, 65, 66, 67, 68, 127,<br>128, 129, 130, 135, 136, 139,<br>140, 141, 142, 145, 146, 151,<br>152, 153, 154, 163, 164, 165,<br>166, 171, 172, 175, 176, 177,<br>178, 181, 182, 187, 188, 189, | DQ0-DQ63 | Input/<br>Output | Data I/Os: Data bus.                                                                                                       |

| 190<br>1, 2                                                                                                                                                                                                                                                                                                    | VREF     | Supply           | SSTL 2 reference voltage.                                                                                                  |

| 9, 10, 21, 22, 33, 34, 36, 45,<br>46, 57, 58, 69, 70, 81, 82, 92,<br>93, 94, 113, 114, 131, 132,<br>143, 144, 155, 156, 157, 167,<br>168, 179, 180, 191, 192                                                                                                                                                   | VDD      | Supply           | Power Supply: +2.6V ±0.1V.                                                                                                 |

| 3, 4, 15, 16, 27, 28, 38, 39, 40,<br>51, 52, 63, 64, 75, 76, 87, 88,<br>90, 103, 104, 125, 126, 137,<br>138, 149, 150, 159, 161, 162,<br>173, 174, 185, 186, 200                                                                                                                                               | Vss      | Supply           | Ground.                                                                                                                    |

| 197                                                                                                                                                                                                                                                                                                            | VDDSPD   | Supply           | Serial EEPROM positive power supply: +2.3V to +3.6V                                                                        |

| 85, 97, 98, 123, 124, 199                                                                                                                                                                                                                                                                                      | NC       | _                | No Connect: These pins should be left unconnected.                                                                         |

| 71, 72, 73, 74, 77, 78, 79, 80,<br>83, 84, 86, 89, 91                                                                                                                                                                                                                                                          | DNU      | _                | Do Not Use: These pins are not connected on this module, but<br>are assigned pins on other modules in this product family. |

SDA

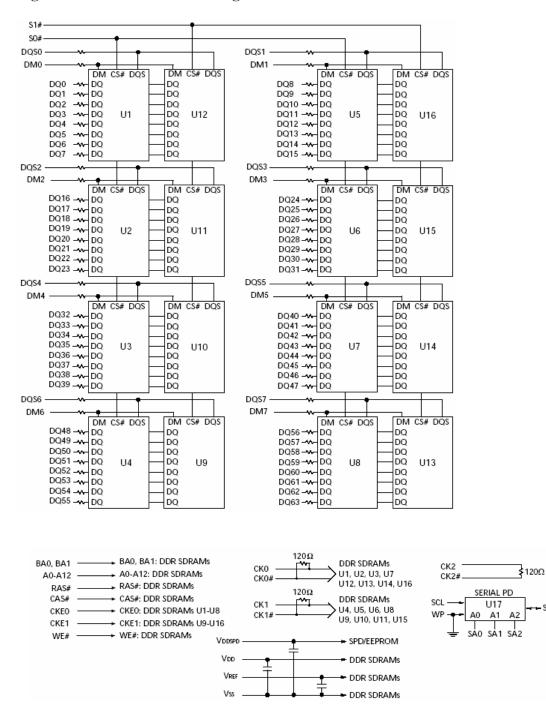

#### Figure 3: Functional Block Diagram – 1GB

#### **General Description**

The D400SB1G\_M is a high-speed CMOS, dynamic random-access, 1GB memory module organized in a x64 configuration. DDR SDRAM modules use internally configured quad-bank DDR SDRAM devices.

DDR SDRAM modules use a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the DDR SDRAM module effectively consists of a single 2n-bit wide, one-clock-cycle data transfer at the internal DRAM core and two corresponding n-bit wide, onehalf-clock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is an intermittent strobe transmitted by the DDR SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs.

DDR SDRAM modules operate from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Read and write accesses to DDR SDRAM modules are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the device bank and row to be accessed (BA0, BA1 select devices bank; A0–A12 select device row). The address bits registered coincident with the READ or WRITE command are used to select the device bank and the starting device column location for the burst access.

DDR SDRAM modules provide for programmable read or write burst lengths of 2, 4, or 8 locations. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access. The pipelined, multibank architecture of DDR SDRAM modules allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

An auto refresh mode is provided, along with a power-saving power-down mode. All inputs are compatible with the JEDEC Standard for SSTL\_2. All outputs are SSTL\_2, Class II compatible.

## **Serial Presence-Detect Operation**

DDR SDRAM modules incorporate serial presencedetect (SPD). The SPD function is implemented using a 2,048-bit EEPROM. This nonvolatile storage device contains 256 bytes. The first 128 bytes can be programmed by the manufacturer to identify the module type and various SDRAM organizations and timing parameters. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the master (system logic) and the slave EEPROM device (DIMM) occur via a standard I2C bus using the DIMM's SCL (clock) and SDA (data) signals, together with SA (2:0), which provide eight unique DIMM/EEPROM addresses. Write protect (WP) is tied to ground on the module, permanently disabling hardware write protect.

# Mode Register Definition

The mode register is used to define the specific mode of operation of DDR SDRAM devices. This definition includes the selection of a burst length, a burst type, a CAS latency and an operating mode. The mode register is programmed via the MODE REGISTER SET command (with BA0 = 0 and BA1 = 0) and will retain the stored information until it is programmed again or the device loses power (except for bit A8, which is self-clearing).

Reprogramming the mode register will not alter the contents of the memory, provided it is performed correctly. The mode register must be loaded (reloaded) when all device banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.

Mode register bits A0–A2 specify the burst length, A3 specifies the type of burst (sequential or interleaved), A4–A6 specify the CAS latency, and A7–A12 specify the operating mode.

|                   |                 |               |                |          |                            |                                      | -                                         |          |      |                                                                                |                                                                                                                        |               |         |

|-------------------|-----------------|---------------|----------------|----------|----------------------------|--------------------------------------|-------------------------------------------|----------|------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------|---------|

| BA1 BA0 A12       | 2 A11           | A10           | A9             | A8       | A7                         | A6                                   | A5                                        | A4 A     | 43 A | 2 A1 A                                                                         | lo Add                                                                                                                 | ress Bu       | s       |

|                   | 1               | 1             | L              | 1        | Ţ                          | 1                                    | 1                                         |          |      |                                                                                |                                                                                                                        |               |         |

|                   | Ţ               | Ţ             | Ţ              | Ţ.       | Ţ                          | Ţ                                    | Ţ                                         | Ţ        | 1    | 1 <b>1</b> 1                                                                   | , I                                                                                                                    |               |         |

| 14/13/12/         | 11/             | 10/1          | 9/             | 8/1      | <u> </u>                   | 6/                                   | 5/                                        | 4/3      | 12   | /1/0                                                                           | Mode                                                                                                                   | Regist        | ər (Mx) |

| 0* 0* 0           | Opera           | ating         | Mod            | e        | C/                         | ۱SLa                                 | itenc                                     | y BT     | Burs | t Length                                                                       |                                                                                                                        |               |         |

| * M14 and M13 (BA | A1 an           | 4 DA4         |                |          |                            |                                      |                                           |          |      |                                                                                |                                                                                                                        |               |         |

| must be "0, 0" to |                 |               | "              |          |                            |                                      |                                           |          |      | 1                                                                              |                                                                                                                        |               |         |

| base mode regist  |                 |               |                |          |                            |                                      |                                           |          |      | _                                                                              | Burst Le                                                                                                               | ength         |         |

| extended mode     | regist          | ter).         |                |          |                            |                                      |                                           |          | M2   | M1 M0                                                                          | M3 =                                                                                                                   | -             |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 0    | 0 0                                                                            | Reserv                                                                                                                 |               |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 0    | 0 1                                                                            | 2                                                                                                                      |               |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 0    | 1 0                                                                            | 4                                                                                                                      |               |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 0    | 1 1                                                                            | 8                                                                                                                      |               |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 1    | 0 0                                                                            | Reserv                                                                                                                 | ed            |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 1    | 0 1                                                                            | Reserv                                                                                                                 | ed            |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 1    | 10                                                                             | Reserv                                                                                                                 | ed            |         |

|                   |                 |               |                |          |                            |                                      |                                           |          | 1    | 11                                                                             | Reserv                                                                                                                 | ed            |         |

|                   |                 |               |                |          |                            |                                      |                                           |          |      |                                                                                |                                                                                                                        |               |         |

|                   |                 |               |                |          |                            |                                      |                                           | <u>t</u> |      |                                                                                |                                                                                                                        |               |         |

|                   |                 | M3 Burst Type |                |          |                            |                                      |                                           |          |      |                                                                                |                                                                                                                        |               |         |

|                   |                 |               |                |          |                            |                                      |                                           | M3       |      |                                                                                | Burst Typ                                                                                                              | )e            |         |

|                   |                 |               |                |          |                            |                                      |                                           | 0        |      |                                                                                | Sequenti                                                                                                               | al            |         |

|                   |                 |               |                |          |                            |                                      |                                           |          |      |                                                                                |                                                                                                                        | al            |         |

|                   |                 |               |                |          | _                          |                                      |                                           | 0        |      |                                                                                | Sequenti<br>Interleav                                                                                                  | al            |         |

|                   |                 |               |                |          | Me                         |                                      | 5 M4                                      | 0        |      | AS Laten                                                                       | Sequenti<br>Interleav<br>cy                                                                                            | al            |         |

|                   |                 |               |                |          | 0                          | 0                                    | 0                                         | 0        |      | Reserved                                                                       | Sequenti<br>Interleav<br>cy                                                                                            | al            |         |

|                   |                 |               |                |          | 0                          | 0                                    | 0                                         | 0        |      | Reserved<br>Reserved                                                           | Sequenti<br>Interleav<br>cy                                                                                            | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0                | 0<br>0<br>1                          | 0<br>1<br>0                               | 0        |      | Reserved<br>Reserved<br>2                                                      | Sequenti<br>Interleav<br>cy                                                                                            | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0                | 0<br>0<br>1<br>1                     | 0<br>1<br>0<br>1                          | 0        |      | Reserved<br>Reserved<br>2<br>3                                                 | Sequenti<br>Interleav<br>cy<br>1                                                                                       | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0<br>1           | 0<br>0<br>1<br>1<br>0                | 0<br>1<br>0<br>1<br>0                     | 0        |      | Reserved<br>Reserved<br>2<br>3<br>Reserved                                     | Sequenti<br>Interleave<br>cy<br>I                                                                                      | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0<br>1           | 0<br>1<br>1<br>0<br>0                | 0<br>1<br>0<br>1<br>0                     | 0        |      | Reserved<br>Reserved<br>2<br>3<br>Reserved<br>Reserved                         | Sequenti<br>Interleave<br>cy<br>I                                                                                      | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0<br>1<br>1      | 0<br>0<br>1<br>0<br>0<br>1           | 0<br>1<br>0<br>1<br>0<br>1<br>0           | 0        |      | Reserved<br>2<br>3<br>Reserved<br>Reserved<br>2.5                              | Sequenti<br>Interleav<br>cy<br>I<br>I<br>I                                                                             | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0<br>1           | 0<br>1<br>1<br>0<br>0                | 0<br>1<br>0<br>1<br>0                     | 0        |      | Reserved<br>Reserved<br>2<br>3<br>Reserved<br>Reserved                         | Sequenti<br>Interleav<br>cy<br>I<br>I<br>I                                                                             | al            |         |

|                   |                 |               |                |          | 0<br>0<br>0<br>1<br>1      | 0<br>0<br>1<br>0<br>0<br>1           | 0<br>1<br>0<br>1<br>0<br>1<br>0           | 0        |      | Reserved<br>2<br>3<br>Reserved<br>Reserved<br>2.5                              | Sequenti<br>Interleav<br>cy<br>I<br>I<br>I                                                                             | al            |         |

|                   | M13             | M12           | 4<br>M11       | M10      | 0<br>0<br>1<br>1<br>1      | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0           | 0        |      | Reserved<br>2<br>3<br>Reserved<br>2.5<br>Reserved<br>2.5                       | Sequenti<br>Interleav<br>cy<br>I<br>I<br>I                                                                             | ed            |         |

|                   | <u>M13</u><br>0 | M12<br>0      | #<br>M111<br>0 | M10<br>0 | 0<br>0<br>1<br>1<br>1      | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0           |          | Mo   | Reserved<br>2<br>3<br>Reserved<br>2.5<br>Reserved<br>2.5<br>Reserved           | Sequenti<br>Interleave<br>cy<br>I<br>I<br>I<br>I                                                                       | al<br>ed      |         |

|                   |                 |               |                |          | 0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>0<br>0<br>1<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | 0<br>1   | Mo   | Reserved<br>2<br>3<br>Reserved<br>2.5<br>Reserved<br>2.5<br>Reserved<br>0perat | Sequenti<br>Interleave<br>Cy<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I | al<br>ed<br>a | at DLL  |

## Figure 4: Mode Register Definition Diagram

#### Commands

The Commands Truth Table provides a general reference of available commands.

#### **Table 6: Commands Truth Table**

CKE is HIGH for all commands shown except SELF REFRESH

| NAME (FUNCTION)                                        | CS# | RAS# | CAS# | WE# | ADDR     | NOTES |

|--------------------------------------------------------|-----|------|------|-----|----------|-------|

| DESELECT (NOP)                                         | Н   | Х    | Х    | Х   | Х        | 1     |

| NO OPERATION (NOP)                                     | L   | Н    | Н    | Н   | Х        | 1     |

| ACTIVE (Select bank and activate row)                  | L   | L    | Н    | Н   | Bank/Row | 2     |

| READ (Select bank and column, and start READ burst)    | L   | н    | L    | Н   | Bank/Col | 3     |

| WRITE (Select bank and column, and start WRITE burst)  | L   | н    | L    | L   | Bank/Col | 3     |

| BURST TERMINATE                                        | L   | Н    | Н    | L   | Х        | 4     |

| PRECHARGE (Deactivate row in bank or banks)            | L   | L    | Н    | L   | Code     | 5     |

| AUTO REFRESH or SELF REFRESH (Enter self refresh mode) | L   | L    | L    | Н   | Х        | 6, 7  |

| LOAD MODE REGISTER                                     | L   | L    | L    | L   | Op-Code  | 8     |

NOTE:

- 1. DESELECT and NOP are functionally interchangeable.

- 2. BA0–BA1 provide device bank address and A0–A12 provide device row address.

- 3. BA0–BA1 provide device bank address; A0–A9, A11 (1GB) provide device column address; A10 HIGH enables the auto precharge feature (nonpersistent), and A10 LOW disables the auto precharge feature.

- 4. Applies only to read bursts with auto precharge disabled; this command is undefined (and should not be used) for READ bursts with auto precharge enabled and for WRITE bursts.

- 5. A10 LOW: BA0-BA1 determines which device bank is precharged. A10 HIGH: all device banks are precharged and BA0–BA1 are "Don't Care."

- 6. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

- 7. Internal refresh counter controls device row addressing; all inputs and I/Os are "Don't Care" except for CKE.

- 8. BA0–BA1 select either the mode register or the extended mode register (BA0 = 0, BA1 = 0 select the mode register; BA0 = 1, BA1 = 0 select extended mode register; other combinations of BA0-BA1 are reserved). A0–A12 provide the op-code to be written to the selected mode register.

## Figure 5: 200-Pin SODIMM Dimensions –1GB